# The analysis and layout of a Switching Mode Power Supply

The more knowledge you have about a switching mode power supply, the better chances your job works on layout.

#### Introductions

The implementation of layout would be different in both **analog** and **digital** fields. Digital designers usually line up the components in neat, logical rows, and the trace on the PCB is mostly as narrow as 8 mil (1 mil=0.001 inch) or less. It would be good to see an aesthetically digital design, but a similarly designed power supply probably doesn't work very well.

However, many analog designers start by dealing with the portions within a circuit, which is most likely to be interfered, and then take care of the output node. Again, it might work well for an analog design, but mostly not suitable for power supply layout design.

Following paragraph is to discuss how to build a correct layout regulation from knowing the operation of a circuit.

# Relationships

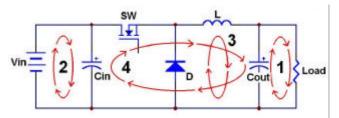

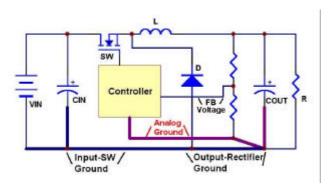

Every switching power supply has four current loops (figure 1). Keep them separate from each other in

various degrees of their interfering capability, they are:[1]

- 1. The output load loop

- 2. The input source loop

- 3. The output rectifier loop

- 4. The power switch loop

Fig 1. The Major Current Loop of a Switching Mode Power Supply

The current flows in both input and output loops are composed of DC elements with some AC ripple current. That means these two loops do not result in problems most of the time. It's easy to get rid of the high frequency switching noise due to some special filter attached. On the other hand, the power switch and rectifier current loops are entirely AC. They have trapezoidal current waveforms with high peak currents and sharp edges (di/dt). We know that those waveforms contain excellent high order harmonic after some mathematical expansion, meanwhile, the EMI takes place.

Let's start from analyzing each loop and developing some relevant layout regulations.

## **Output loop**

The output current stays at a constant state due to the balance between inductor current and capacitor current (both of the charge and discharge current) during the power switch ON and OFF. The charge and discharge effect in capacitor form a ripple voltage on output node. Also, along with the effect of ESR (Equivalent Series Resistance) and ESL (Equivalent Series Inductance), the transient response is not as healthy as we expect. Therefore, it's helpful to eliminate the effect of ESR and ESL, which take care of the trace width and shorten the trace length between the filter capacitor and the load.

Fig 2. AIC1340 Synchronous Rectifier Buck Converter Example

#### Input loop

VIC

An adequate capacitor value, in parallel with power source of the system, is required due to the power source, which usually unable to provide the instantaneous large current. Besides, to prevent the spike voltage from feeding back to the power line, some isolated installation should be placed, for example, a small inductor between power source and power switch.

#### **Rectifier and Power switch loop**

Since a large loop current flows during the switching operation, the EMI occurrs. The reduction of the size of these two high current loops results in two advantages as follows:

- 1. Generating less radiation.

- Producing less magnetic coupling between adjacent circuitry. Moreover, a designed trace size to handle peak current along with proper grounding of the control stage is profitable to the system.

#### **Examples**

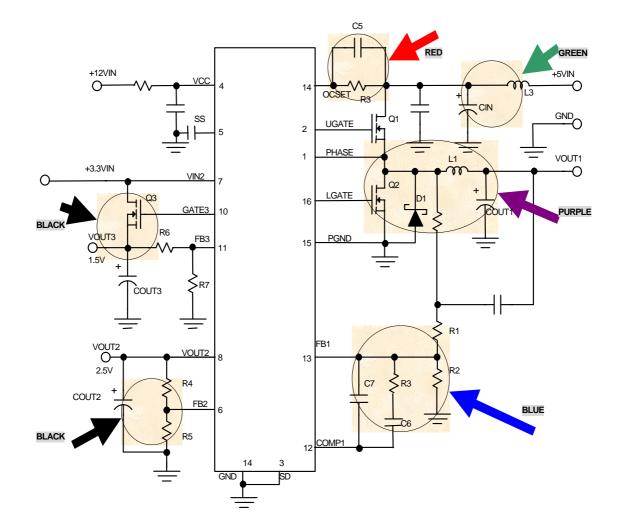

A complete system consists of not only the above four loops but also some additional functions. Accordingly, the layout gets more complicated. AIC1340 shown in figure 2 is a PWM controller  $IC_{[3]}$ that contains a synchronous rectifier buck converter, a low dropout regulator (LDO) and an LDO controller. Along with the built-in voltage monitoring and over-current protection, the use of IC gets more flexible. These features make AIC's PWM controller IC more powerful.

The following table represents the functions according to the highlighted circles in figure 2, which are pointed with arrows in different colors, respectively:

| Color |        | Function               | Parts                                               |

|-------|--------|------------------------|-----------------------------------------------------|

|       | Purple | Power stage and output | Q1,Q2,L1,C <sub>OUT1</sub> ,D1                      |

|       |        | loop                   |                                                     |

|       | Green  | Input filter           | C <sub>IN</sub> ,L3                                 |

|       | Black  | LDO output             | Q3,R4,R5,R6,R7,C <sub>OUT2</sub> ,C <sub>OUT3</sub> |

|       | Red    | Over-current detect    | C5,R3                                               |

|       | Blue   | Voltage feedback       | R1,R2,R3,C6,C7                                      |

Table 1.PWM Controller Functions

# AN017

#

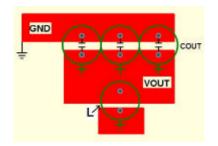

The purple segment is the rectifier and power switch loop as described before. The only difference here is the implementation of synchronous rectifier structure, which improves the efficiency performance a lot. For the layout considerations, care must be taken to make sure the power stage components such as Q1, Q2, L1 and COUT1 as close as possible. Designers sometimes use parallel capacitors in the output filter to minimize voltage ripple in the load and to reduce the circuit's total resistance. However, it's important to ensure that the first parallel capacitor doesn't overheat from conducting a ripple current, which is higher than others. Furthermore, the power trace and return trace in the output stage should be as close as possible. They minimize the loop area between the two traces and increase coupling capacitors, as shown in figure 3.[4]

Fig 3. The Placement and Layout on Switching Output Node

- The green segment only is composed of CIN and L3, yet a proper trace width requires. In addition, the recommended capacitor voltage rating should be at least two times as the input voltage. A de-coupling ceramic attached between CIN and ground is helpful to eliminate the high frequency noise.

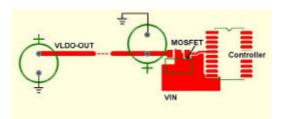

- The black segment consists of an LDO and an LDO controller. By minimizing the voltage feedback loop length, the unnecessary interference can be avoided. In case the output trace is too long, an extra-capacitor attachment on the end of the output node, as shown in figure 4, prevents the LDO from unstable oscillation.

Fig 4. The placement and layout on LDO output node

The red segment, over-current protection, is very sensitive to pick up the noise from switching. The limitation of the maximum current flows through MOSFET is to compare with an internal standard 200uA sink current. Therefore, a clear detection source is required to have a precise protection. Extending the length of the trace and adding a de-coupling capacitor to ground will be recommended.

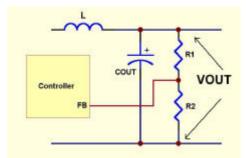

The blue segment acts as a voltage feedbacker.

As figure 5 shows,

Figure 5. The voltage feedbacker

The feedback path from output node through resistor divider to IC's FB pin is a low-impedance route, because its Thevenin equivalent resistance equals to  $(R1+R2)//R_{FB}$ . The resistance is close to R1+R2, which is 1000-ohm degree. On the other hand, the equivalent resistance equals to the high impedance OP-Amp input R<sub>FB</sub>. From the viewpoint of IC controller, the high impedance is typically a several hundred-thousand-ohm degree. The path from resistor divider to error amplifier should be as short as possible and consists of parallel paths to reduce noise pick-up. Moreover, take the utmost care to avoid the interlace arrangement between feedbacker and large current plane.

The same principles are able to imitate on other switching topologies, such as boost and flyback structure.

## Grounding

The ground, a very important function, serves as a common point of reference for the circuitry. Therefore, to place the ground carefully is crucial since the carelessness will cause instability in the power supply.

There are three grounds within a switching mode power supply:

- 1. the input high current ground

- 2. output high current ground

- control stage ground, which is shown in figure

6 below.[1]

Figure 6. The Grounding Arrangement of PWM Buck Topology

Some ICs use the separated analog and power ground pins on pin arrangement. The analog ground should be connected to a clearer one, as it serves as a consultation point of the voltage reference. The precise voltage reference inside controller has significant influences on the stability of the output voltage directly.

Another good implementation to reduce EMI is to place a large ground plane on PCB back side. The ground plane plays a role as a wall to prevent some RF energy from radiating to the environment. Furthermore, it gains the thermal characteristics to keep the PCB at a lower temperature (Comparing to no planes).

# Conclusions

According to the characteristics of a switching mode power supply, following steps summarize the process on designing power supply PCB layout.

- 1. Place the inductor (Transformer) first.

- 2. Power switch and rectifier loop such as SW, D,  $$C_{\text{OUT}}$$

- 3. IC controller and peripheral

- 4. Output loop

- 5. Input loop

Among a system design, the power is usually remained to be the last part with a limited space, which becomes a challenge for a layout designer. Then the value of layout designers emerges from the requirement, doesn't it?

# Reference

- Designing PCBs for embedded switching power supplies, Marty Brown, Electronics Engineer December/1999

- [2]. The effect of ESR on DC/DC power converter, , Stanley Chen, Compotech Vol19, p142~p148

- [3]. AIC1340 Data Sheet, Analog integrations Corporation, AIC 2000

- [4]. Board layout boosts power-supply performance, Philip Rogers, EDN, November/1998, p176