# 600mA Ultra Low I<sub>Q</sub> Step-down DC/DC Converter With AOT Control

#### **FEATURES**

- Typ. 700nA Quiescent Current

- Adaptive On Time Control

- 2.5V to 5.5V Input Range

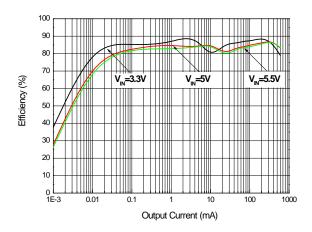

- Up to 91% Efficiency

- 16 Selectable Output Voltages in 100mV Steps between 1.8V to 3.3V

- Up to 600mA Output Current

- Automatic Transition to No Ripple 100% Mode

- Low Output Ripple Voltage

- Slew Rate Controlled Load Switch

- Discharge Function on VOUT / LOAD

- Power Good Output

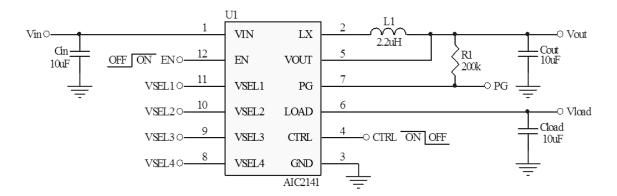

- Optimized for Operation with a Tiny 2.2 $\mu$ H Inductor and 10 $\mu$ F C<sub>OUT</sub>

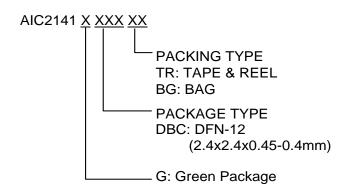

- Small 2.4 x 2.4 mm<sup>2</sup> DFN-12 Package

### **APPLICATIONS**

- Wearable Device

- Bluetooth Low Energy

- Sensor HUB

- RF Module

#### DESCRIPTION

The AIC2141 is ultra low Io step-down dc/dc converter featuring typical 700nA quiescent current and operating with a tiny 2.2µH inductor and 10µF output capacitor. AIC2141 based device extends the light load efficiency range below 10µA load currents. AIC2141 supports output currents up to 600mA. The input voltage range from 2.5V to 5.5V allows also operation from a USB port and thin-film solar modules. The output voltage is user selectable by four VSEL pins within a range from 1.8V to 3.3V in 100mV steps. AIC2141 features low output ripple voltage and low noise with a small output capacitor. Once the battery voltage comes close to the output voltage (close to 100% duty cycle) the device enters no ripple 100% mode operation to prevent an increase of output ripple voltage. The device then stops switching and the output is connected to the input voltage. The integrated slew rate controlled load switch provides typical  $0.6\Omega$  on-resistance and can distribute the selected output voltage to a temporarily used sub-system. The AIC2141 is available in a small 12 pin 2.4 x 2.4mm<sup>2</sup> DFN-12 package.

#### ■ APPLICATIONS CIRCUIT

AIC2141 Application Circuit

**Analog Integrations Corporation**

Si-Soft Research Center

DS-2141G-02 20200831

1

1A1, No.1, Li-Hsin Rd. I, Science Park, Hsinchu 300, Taiwan, R.O.C

TEL: 886-3-5772500 FAX: 886-3-5772510 www.analog.com.tw

## ORDERING INFORMATION

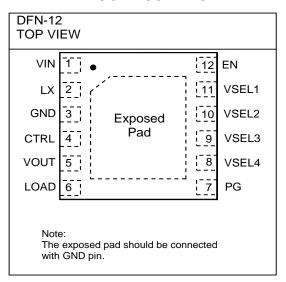

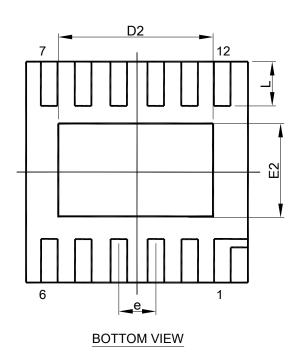

#### PIN CONFIGURATION

Example: AIC2141GDBCTR

→ in DFN-12 Green Package and Tape

& Reel Packing Type

## ■ ABSOLUTE MAXIMUM RATINGS

| Supply Input Volatge, V <sub>IN</sub>      |                       | 6.0V          |

|--------------------------------------------|-----------------------|---------------|

| Pin Voltage for VOUT, LOAD                 |                       | -0.3V to 3.7V |

| Pin Voltage for all other Pins             |                       |               |

| Operating Ambient Temperature Range T      | A                     | -40°C to 85°C |

| Operating Maximum Junction Temperature     | e T <u>J</u>          | 150°C         |

| Storage Temperature Range T <sub>STG</sub> |                       | 65°C to 150°C |

| Lead Temperature (Soldering 10 Sec.)       |                       | 260°C         |

| Thermal Resistance Junction to Case        |                       | 10°C/W        |

| Thermal Resistance Junction to Ambient     | DFN-12L (2.4x2.4 mm)* | 65°C/W        |

| (Assume no Ambient Airflow)                |                       |               |

Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

<sup>\*</sup>The package is place on a two layers PCB with 2 ounces copper and 2 square inch, connected by 8 vias.

# **ELECTRICAL CHARACTERISTICS**

( $V_{IN}$ =3.6V, unless otherwise specified. Typical values are at  $T_A$ =25°C)

| PARAMETER                                         | SYMBOL                                | CONDITIONS                                                                                                                                           | MIN | TYP  | MAX  | UNITS |

|---------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| Supply                                            |                                       |                                                                                                                                                      |     |      |      |       |

| Operating Voltage                                 | V <sub>IN</sub>                       |                                                                                                                                                      | 2.5 |      | 5.5  | V     |

| Shutdown Current                                  | I <sub>SHDN</sub>                     | V <sub>EN</sub> =0V, shutdown current into V <sub>IN</sub>                                                                                           |     | 70   | 1000 | nA    |

| Quiescent Current                                 | IQ                                    | V <sub>EN</sub> =High, CTRL=GND, I <sub>OUT</sub> =0mA, V <sub>OUT</sub> =1.8V, device not switching                                                 |     | 700  | 1500 | nA    |

| Logic Threshold                                   | 1                                     |                                                                                                                                                      |     | I    | l .  |       |

| EN, CTRL, VSEL1-4<br>High Level Input<br>Voltage  | V <sub>H</sub>                        | 2.5V≤ V <sub>IN</sub> ≤ 5.5V                                                                                                                         |     |      | 1.1  | V     |

| EN, CTRL, VSEL1-4<br>Low Level Input Volt-<br>age | V <sub>L</sub>                        | 2.5V ≤ V <sub>IN</sub> ≤ 5.5V                                                                                                                        | 0.4 |      |      | V     |

| Output Discharge Sv                               | vitch (VOUT)                          |                                                                                                                                                      |     |      |      |       |

| MOSFET on-<br>resistance                          | R <sub>DSCH_VOUT</sub>                | $V_{IN} = 3.6V$ , EN = GND, $I_{OUT} = -10$ mA into VOUT pin                                                                                         |     | 10   | 30   | Ω     |

| Bias current into VOUT pin                        | I <sub>IN_VOUT</sub>                  | $V_{IN} = 3.6V$ , EN = High, $V_{OUT} = 2V$ , CTRL =GND                                                                                              |     | 130  | 200  | nA    |

| Load Output (LOAD)                                |                                       |                                                                                                                                                      |     | •    |      |       |

| R <sub>LOAD</sub>                                 | High Side<br>MOSFET on-<br>resistance | $I_{LOAD}$ = 50mA, CTRL = High, VOUT = 2.0V, 2.5V $\leq$ $V_{IN} \leq$ 5.5V                                                                          |     | 0.8  | 1.25 | Ω     |

| R <sub>RDSCH_LOAD</sub>                           | Low Side<br>MOSFET on-<br>resistance  | CTRL = GND, $2.5V \le V_{IN} \le 5.5V$ , $I_{LOAD} = -10mA$                                                                                          |     | 10   | 30   | Ω     |

| <sup>†</sup> Rise_LOAD                            | V <sub>LOAD</sub> rise<br>time        | Starting with CTRL low to high transition, time to ramp $V_{LOAD}$ from 0V to 95% $V_{OUT}$ = 1.8V, 2.5V $\leq$ $V_{IN} \leq$ 5.5V, $I_{LOAD}$ = 1mA |     | 200  | 800  | μs    |

| Auto 100% Mode Transition                         |                                       |                                                                                                                                                      |     |      |      |       |

| Auto 100% Mode<br>leave detection<br>threshold    | V <sub>TH_100+</sub>                  | Rising $V_{IN}$ ,100% Mode is left with $V_{IN} = V_{OUT} + V_{TH_100+}$ , max value at $T_J = 85^{\circ}C$                                          |     | 250  |      | mV    |

| Auto 100% Mode enter detection threshold          | V <sub>TH_100</sub> -                 | Fallinf $V_{IN}$ , 100% Mode is entered with $V_{IN} = V_{OUT} + V_{TH\_100-}$ , max value at $T_J = 85^{\circ}C$                                    |     | 250  |      | mV    |

| Switch On Resistance                              |                                       |                                                                                                                                                      |     |      |      |       |

| High Side Switch On Resistance                    | R <sub>DS(ON)H</sub>                  | V <sub>IN</sub> = 3.6V, lout = 50mA                                                                                                                  |     | 0.55 | 0.85 | Ω     |

| Low Side Switch On Resistance                     | R <sub>DS(ON)L</sub>                  | V <sub>IN</sub> = 3.6V, lout = 50mA                                                                                                                  |     | 0.22 | 0.5  | Ω     |

# ■ ELECTRICAL CHARACTERISTICS (Continuous)

| PARAMETER                                        | SYMBOL                     | CONDITIONS                                                                                                   |                      |    | TYP   | MAX  | UNITS |

|--------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------|----------------------|----|-------|------|-------|

| Output                                           |                            |                                                                                                              |                      |    |       |      |       |

| Output Voltage<br>Range                          |                            | Output voltages are selected with pins VSEL 1 - 4                                                            |                      |    |       | 3.3  | V     |

| Output Voltage Accuracy                          | $V_{OUT}$                  | V <sub>IN</sub> = 3.6V,VOUT=1.8V                                                                             |                      | -2 |       | 2    | %     |

| Line Regulation                                  |                            | $V_{OUT} = 1.8V$ , CTRL = $V_{IN}$ , $I_{OUT} = 10$ mA, $2.5V \le V_{IN}$ $\le 5.5V$                         |                      |    | 0.1   |      | %/V   |

| Load Regulation                                  |                            | $V_{OUT} = 1.8V, V_{IN} = 3.6V, CTRL = V$                                                                    | $V_{IN}$             |    | 0.005 |      | %/mA  |

| Regulator start up delay time                    | t <sub>Startup_delay</sub> | $V_{IN} = 3.6V$ , from transition EN = k device starts switching                                             | ow to high until     |    | 2.5   | 5    | ms    |

| Softstart time with reduced switch current limit | t <sub>Softstart</sub>     | $2.5V \le V_{IN} \le 5.5V, EN = V_{IN}$                                                                      |                      |    | 800   | 1200 | μs    |

| High side MOSFET switch current limit            | I <sub>LIM_softstart</sub> | Reduced switch current limit during softstart                                                                |                      | 80 | 150   |      | mA    |

| <b>Current Limit</b>                             |                            |                                                                                                              |                      |    |       |      |       |

| High Side Switch<br>Forward Current Lim-<br>it   | I <sub>LIMIT</sub>         | V <sub>IN</sub> =3.6V                                                                                        |                      |    | 850   |      | mA    |

| On-Time Timer Contr                              | ol                         |                                                                                                              |                      |    |       |      |       |

| Minimum On-Time                                  | $t_{ON}$                   | $V_{IN}$ =3.6V, $V_{OUT}$ =1.8V                                                                              |                      |    | 333   |      | ns    |

| Minimum Off-Time                                 | t <sub>OFF(MIN)</sub>      | V <sub>IN</sub> =2.5V                                                                                        |                      |    | 60    |      | ns    |

| Power Good                                       |                            |                                                                                                              |                      |    |       |      |       |

| PGOOD Threshold                                  | $V_{TH\_PG}$               | Rising output voltage on VOUT pin, referred to $V_{\text{VOUT}}$                                             |                      |    | 97.5  |      | %     |

|                                                  | V <sub>PG Hys</sub>        | Hysteresis                                                                                                   |                      |    | 2     |      |       |

| PGOOD Output Low                                 | $V_{OL\_PG}$               | $2.5V \le V_{IN} \le 5.5V$ , EN=GND, current into PG pin $I_{PG} = 4mA$                                      |                      |    |       | 0.3  | V     |

| Bias Current Into PG<br>Pin                      | I <sub>IN_PG</sub>         | PG pin is high impedance,<br>V <sub>OUT</sub> =2V, EN=V <sub>IN</sub> , CTRL =<br>GND, I <sub>OUT</sub> =0mA | T <sub>A</sub> =25°C |    | 0     | 10   | nA    |

| Under Voltage Lockout Voltage                    |                            |                                                                                                              |                      |    |       |      |       |

| UVLO Threshold                                   | $V_{\text{UVLO+}}$         | Raising Input Voltage                                                                                        |                      |    | 2.15  | 2.45 | V     |

| O VEO TINOSTIOIO                                 | $V_{UVLO}$                 | Falling Input Voltage                                                                                        |                      |    | 1.95  | 2.4  | V     |

Note 1: Specifications are production tested at T<sub>A</sub>=25°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with Statistical Quality Controls (SQC).

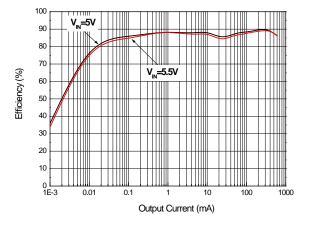

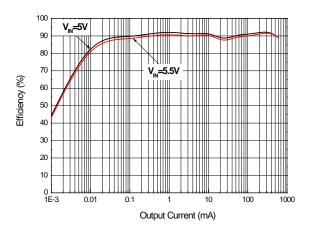

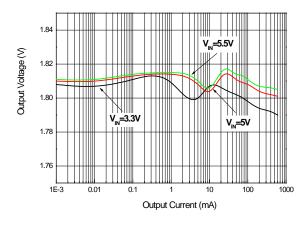

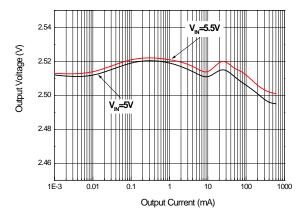

## ■ TYPICAL PERFORMANCE CHARACTERISTICS

Fig. 1 Efficiency vs. Output Current (V<sub>OUT</sub>=1.8V)

Fig. 2 Efficiency vs. Output Current (V<sub>OUT</sub>=2.5V)

Fig. 3 Efficiency vs. Output Current (V<sub>OUT</sub>=3.3V)

Fig. 4 Output Voltage vs. Output Current (V<sub>OUT</sub>=1.8V)

Fig. 5 Output Voltage vs. Output Current ( $V_{OUT}$ =2.5V)

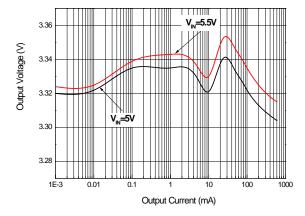

Fig. 6 Output Voltage vs. Output Current (V<sub>OUT</sub>=3.3V)

# TYPICAL PERFORMANCE CHARACTERISTICS (Continuous)

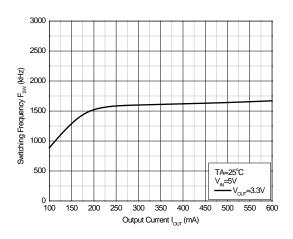

Fig. 7 Frequency vs. Output Current

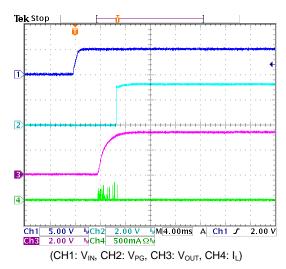

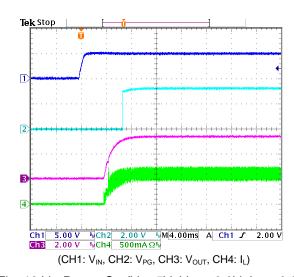

Fig. 9  $V_{IN}$  Power On ( $V_{IN}$ =5V,  $V_{OUT}$ =3.3V,  $I_{OUT}$ =0A)

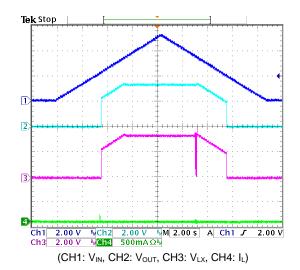

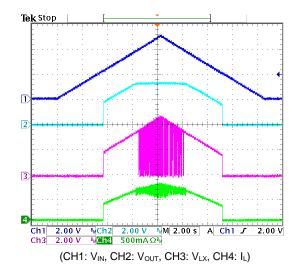

Fig. 11 100% Duty Cycle (V<sub>IN</sub>=0~5V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=0A)

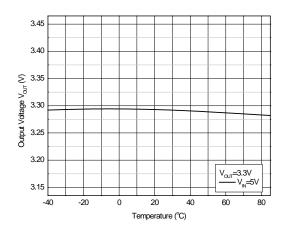

Fig. 8 Output Voltage vs. Temperature

Fig. 10  $V_{IN}$  Power On ( $V_{IN}$ =5V,  $V_{OUT}$ =3.3V,  $I_{OUT}$ =0.6A)

Fig. 12 100% Duty Cycle ( $V_{IN}=0\sim5V$ ,  $V_{OUT}=3.3V$ ,  $I_{OUT}=0.6A$ )

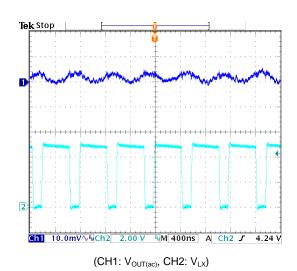

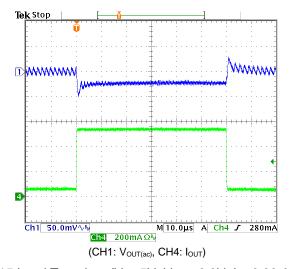

# **■ TYPICAL PERFORMANCE CHARACTERISTICS (Continued)**

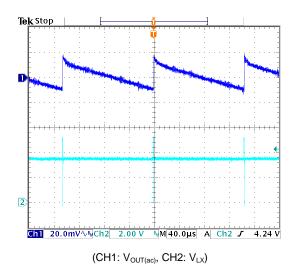

Fig. 13 Output Ripple (V<sub>IN</sub>=5V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=1mA)

Fig. 14 Output Ripple (V<sub>IN</sub>=5V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=0.6A)

Fig. 15 Load Transient ( $V_{IN}$ =5V,  $V_{OUT}$ =3.3V,  $I_{O}$ =0.06-0.54A)

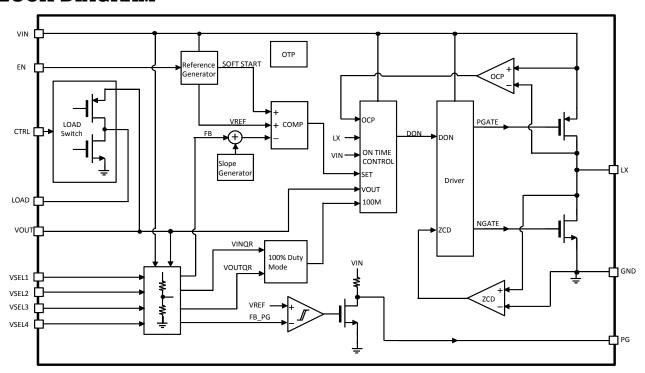

# ■ BLOCK DIAGRAM

**Functional Block Diagram of AIC2141**

# **■ PIN DESCRIPTIONS**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                              |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VIN      | Power Input Supply. Decouple this pin to GND with a capacitor.                                                                                                                                                            |

| 2          | LX       | Internal Power MOSFET Switches Output. Connect this pin to the inductor.                                                                                                                                                  |

| 3          | GND      | Ground. Connect this pin to the negative terminal of C <sub>IN</sub> , C <sub>OUT</sub> and C <sub>LOAD</sub> .                                                                                                           |

| 4          | CTRL     | The LOAD output control pin. The LOAD output is disabled when CTRL is low. This pin isn't allowed to float.                                                                                                               |

| 5          | VOUT     | Output Voltage Sense Pin. An internal power switch is connected between this pin and the LOAD pin. Connect this pin directly to the output capacitor with a short trace.                                                  |

| 6          | LOAD     | The LOAD output. An internal power switch connects the LOAD pin to the VOUT pin when CTRL is high. The LOAD output is connected to GND by an internal discharge switch when CTRL is low. If not used, leave the pin open. |

| 7          | PG       | Power Good Indicator.                                                                                                                                                                                                     |

| 8          | VSEL4    | Output voltage selection pin.                                                                                                                                                                                             |

| 9          | VSEL3    | Output voltage selection pin.                                                                                                                                                                                             |

| 10         | VSEL2    | Output voltage selection pin.                                                                                                                                                                                             |

| 11         | VSEL1    | Output voltage selection pin.                                                                                                                                                                                             |

| 12         | EN       | Enable Pin. Connect to logic high in normal operation. Forcing this ping to GND causes the device to be shutdown. This pin isn't allowed to float.                                                                        |

## APPLICATION INFORMATION

The AIC2141 is an adaptive on-time control synchronous step down converter that can maintain almost fixed switching frequency over full input voltage range. It can deliver up to 600mA output current from 2.5V to 5.5V input voltage. Unlike the traditional fixed frequency PWM control, the adaptive on-time control has the simpler control circuit and the faster transient response. During normal operation, the AIC2141 can regulate its output voltage through a feedback control circuit, which is composed of a comparator, a slope generator, a reference generator and several control signal generators. At the beginning of the switching cycle, the main power switch will be turned on and the synchronous power switch will be turned off. The main power switch will be turned off after the internal on-time timer expires. When the main power switch is turned off, the synchronous power switch will be turned on until the summing signal of feedback voltage signal and slope signal is lower than reference voltage signal or the inductor current starts to reverse. The AIC2141 will enter discontinuous conduction mode (DCM) operation while working at light load conditions.

#### **CTRL**

When CTRL pin is set logic high, an internal power switch will connect the VOUT pin to the LOAD pin to power up an additional sub-system. By connecting the CTRL to GND, the LOAD pin will be disconnected from the VOUT pin and connected to GND by an internal discharge switch. At this operation mode, the voltage of LOAD pin will reduce to 0V.

#### **Enable**

When EN pin is set logic high, AIC2141 is put into active mode operation. By connecting the EN pin to GND, the device can be shutdown to reduce the supply to  $0.07\mu A$  (typical). At this operation mode, the VOUT pin is connected to GND by an internal

discharge switch and the output voltage of step-down converter will reduce to 0V.

#### Soft Start

AIC2141 provides the soft-start function to prevent a large inrush current and output overshoot during start up period. During the soft-start period, the soft-start signal will limit the feedback threshold voltage at FB pin. When the soft-start signal voltage is higher than reference voltage, the feedback threshold voltage at FB pin reaches the desired value. The soft-start time is about 800µs (typical).

#### **Power Good Indictor**

AIC2141 contains an on-chip comparator for power good detection. If the output voltage is lower than power good low threshold, the output voltage of PG pin will be pulled low.

#### **Over Current Protection**

The AIC2141 provides cycle-by-cycle current limit function by using an internal over current protection circuit. When the main power switch turns on, the inductor current follows through the main power switch and the internal over current protection circuit senses it. While the peak value of inductor current gets higher than current limit threshold, the current limitation function is activated. While the current limitation function is activated, cycle-by-cycle current limit protection directly limits inductor peak current to protect the internal power switches.

#### 100% Duty Cycle Operation

When the input voltage falls below the 100% duty cycle mode enter threshold, the AIC2141 will stop switching and enter 100% duty cycle operation mode. In 100% duty cycle mode, the output voltage is equal to the input voltage minus the voltage, which is the drop across the main power switch and the inductor.

The AIC2141 will exit from the 100% duty cycle operation mode and start switching again once the input voltage gets higher than the 100% duty cycle mode leave threshold.

#### **Components Selection**

#### Inductor

A  $2.2\mu H$  inductor is recommended for most AIC2141 applications. Although small size and high efficiency are major concerns, the inductor should have low core losses at operation frequency and low ESR. For most designs, the inductance value can be derived from the following equations:

$$L \ge \frac{V_{OUT}}{f_{OSC} \cdot \Delta I_{I}} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

Where  $\Delta I_{\perp}$  is the inductor ripple current.

In addition, it is important to ensure the inductor saturation current exceeds the peak value of inductor current in application to prevent core saturation. The peak inductor current can be calculated from:

$$I_{\text{PEAK}} = I_{\text{OUT}(\text{max})} + \frac{V_{\text{OUT}}}{2 \! \times \! f_{\text{OSC}} \cdot \! L} \! \left( 1 \! - \! \frac{V_{\text{OUT}}}{V_{\text{IN}}} \right)$$

#### **Input Capacitor Selection**

To prevent the high input voltage ripple and noise resulted from high frequency switching, the use of low ESR ceramic capacitor for the maximum RMS current is recommended. The approximated RMS current of the input capacitor can be calculated according to the following equation.

$$I_{\text{CINRMS}} \approx \sqrt{I_{\text{OUT}(\text{MAX})}^2 \times \frac{V_{\text{OUT}} \left(V_{\text{IN}} - V_{\text{OUT}}\right)}{V_{\text{IN}}^2} + \frac{\Delta I_L^2}{12}}$$

Low ESR, X5R or X7R, ceramic capacitors are ideal for this function. The capacitor should be placed as close to the IC as possible for the best. At least a

$10\mu F$  ceramic capacitor is suggested for the input capacitor.

#### **Output Capacitor Selection**

The selection of output capacitor depends on the required output voltage ripple. The output voltage ripple can be expressed as:

$$\Delta V_{\text{OUT}} = \frac{\Delta I_{\text{L}}}{8 \times f_{\text{OSC}} \cdot C_{\text{OUT}}} + \text{ESR} \cdot \Delta I_{\text{L}}$$

The output capacitor limits the output ripple during large load transient. For low output voltage ripple, the use of low ESR, X5R or X7R, ceramic capacitor is recommended. When choosing output capacitors, the voltage rating of output capacitor should be higher than the output voltage.  $10\mu F$  ceramic capacitor may be needed for the output capacitor.

#### **Setting the Output Voltage**

The AIC2141 doesn't require an external resistor divider to set the output voltage. The output voltage can be programmed by the output voltage selection pins. AIC2141 supports an output voltage range of 1.8V to 3.3V in 0.1V steps. The output voltage can be set according to Table 1.

Table 1 Output Voltage Setting

| V <sub>OUT</sub> (V) | VSEL4 | VSEL3 | VSEL2 | VSEL1 |

|----------------------|-------|-------|-------|-------|

| 1.8                  | Low   | Low   | Low   | Low   |

| 1.9                  | Low   | Low   | Low   | High  |

| 2.0                  | Low   | Low   | High  | Low   |

| 2.1                  | Low   | Low   | High  | High  |

| 2.2                  | Low   | High  | Low   | Low   |

| 2.3                  | Low   | High  | Low   | High  |

| 2.4                  | Low   | High  | High  | Low   |

| 2.5                  | Low   | High  | High  | High  |

| 2.6                  | High  | Low   | Low   | Low   |

| 2.7                  | High  | Low   | Low   | High  |

| 2.8                  | High  | Low   | High  | Low   |

| 2.9                  | High  | Low   | High  | High  |

| 3.0                  | High  | High  | Low   | Low   |

| 3.1                  | High  | High  | Low   | High  |

| 3.2                  | High  | High  | High  | Low   |

| 3.3                  | High  | High  | High  | High  |

## **PCB Layout Guidance**

In order to ensure a proper operation of AIC2141, the following points should be managed comprehensively.

- The input capacitor and V<sub>IN</sub> should be placed as close as possible to each other to reduce the input voltage ripple and noise.

- 2. The output loop, which is consisted of the inductor, the internal power switches and the output capacitor, should be kept as small as possible.

- 3. The routes with large current should be kept

short and wide.

- 4. Logically the large current on the converter should flow at the same direction.

- In order to prevent the effect from noise, the IC's GND pin should be placed close to the ground of the input bypass capacitor.

- The VOUT pin should be connected to the output capacitor directly with a short trace and the route should be away from the noise sources.

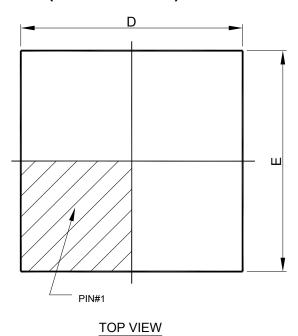

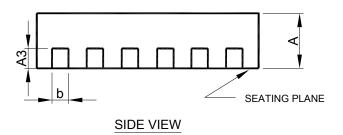

# PHYSICAL DIMENSIONS (unit: mm)

## ● DFN-12 (2.4x2.4x0.45-0.4)

Note: 1. DIMENSION AND TOLERANCING CONFORM TO ASME Y14.5M-1994. 2.CONTROLLING DIMENSIONS: MILLIMETER, CONVERTED INCH DIMENSION ARE NOT NECESSARILY EXACT.

| S           | DFN-12 (2.4) | N-12 (2.4x2.4x0.45-0.4) |  |  |

|-------------|--------------|-------------------------|--|--|

| M<br>B<br>O | MILLIMETERS  |                         |  |  |

| O<br>L      | MIN.         | MAX.                    |  |  |

| Α           | 0.40         | 0.50                    |  |  |

| А3          | 0.127 BSC    |                         |  |  |

| b           | 0.13         | 0.25                    |  |  |

| D           | 2.35         | 2.45                    |  |  |

| D2          | 2.10         | 2.30                    |  |  |

| Е           | 2.35         | 2.45                    |  |  |

| E2          | 1.20 1.40    |                         |  |  |

| е           | 0.40 BSC     |                         |  |  |

| L           | 0.30         | 0.40                    |  |  |

#### Note:

Information provided by AIC is believed to be accurate and reliable. However, we cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AIC product; nor for any infringement of patents or other rights of third parties that may result from its use. We reserve the right to change the circuitry and specifications without notice.

Life Support Policy: AIC does not authorize any AIC product for use in life support devices and/or systems. Life support devices or systems are devices or systems which, (I) are intended for surgical implant into the body or (ii) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.